Search Results for author: Jiansong Zhang

Found 6 papers, 1 papers with code

Evaluation of Infrastructure-based Warning System on Driving Behaviors-A Roundabout Study

no code implementations • 6 Dec 2023 • Cong Zhang, Chi Tian, Tianfang Han, Hang Li, Yiheng Feng, Yunfeng Chen, Robert W. Proctor, Jiansong Zhang

A real-world roundabout in Ann Arbor, Michigan was built in the co-simulation platform as the study area, and the merging scenarios were investigated.

From Pretext to Purpose: Batch-Adaptive Self-Supervised Learning

no code implementations • 16 Nov 2023 • Jiansong Zhang, Linlin Shen, Peizhong Liu

We suggest that the proposed method may contribute to the advancement of data-driven self-supervised learning research, bringing a fresh perspective to this community.

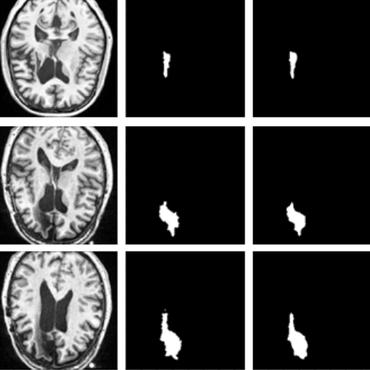

Multi-source adversarial transfer learning for ultrasound image segmentation with limited similarity

no code implementations • 30 May 2023 • Yifu Zhang, Hongru Li, Tao Yang, Rui Tao, Zhengyuan Liu, Shimeng Shi, Jiansong Zhang, Ning Ma, Wujin Feng, Zhanhu Zhang, Xinyu Zhang

Transfer learning provides the possibility to solve this problem, but there are too many features in natural images that are not related to the target domain.

Multi-source adversarial transfer learning based on similar source domains with local features

no code implementations • 30 May 2023 • Yifu Zhang, Hongru Li, Shimeng Shi, Youqi Li, Jiansong Zhang

In order to ensure that the data from the target domain in different sub-networks in the same batch is exactly the same, we designed a multi-source domain independent strategy to provide the possibility for later local feature fusion to complete the key features required.

The Spike Gating Flow: A Hierarchical Structure Based Spiking Neural Network for Online Gesture Recognition

1 code implementation • 4 Jun 2022 • Zihao Zhao, Yanhong Wang, Qiaosha Zou, Tie XU, Fangbo Tao, Jiansong Zhang, Xiaoan Wang, C. -J. Richard Shi, Junwen Luo, Yuan Xie

At last, we conclude the few-shot learning paradigm of the developed network: 1) a hierarchical structure-based network design involves human prior knowledge; 2) SNNs for content based global dynamic feature detection.

MicroRec: Efficient Recommendation Inference by Hardware and Data Structure Solutions

no code implementations • 12 Oct 2020 • Wenqi Jiang, Zhenhao He, Shuai Zhang, Thomas B. Preußer, Kai Zeng, Liang Feng, Jiansong Zhang, Tongxuan Liu, Yong Li, Jingren Zhou, Ce Zhang, Gustavo Alonso

MicroRec accelerates recommendation inference by (1) redesigning the data structures involved in the embeddings to reduce the number of lookups needed and (2) taking advantage of the availability of High-Bandwidth Memory (HBM) in FPGA accelerators to tackle the latency by enabling parallel lookups.